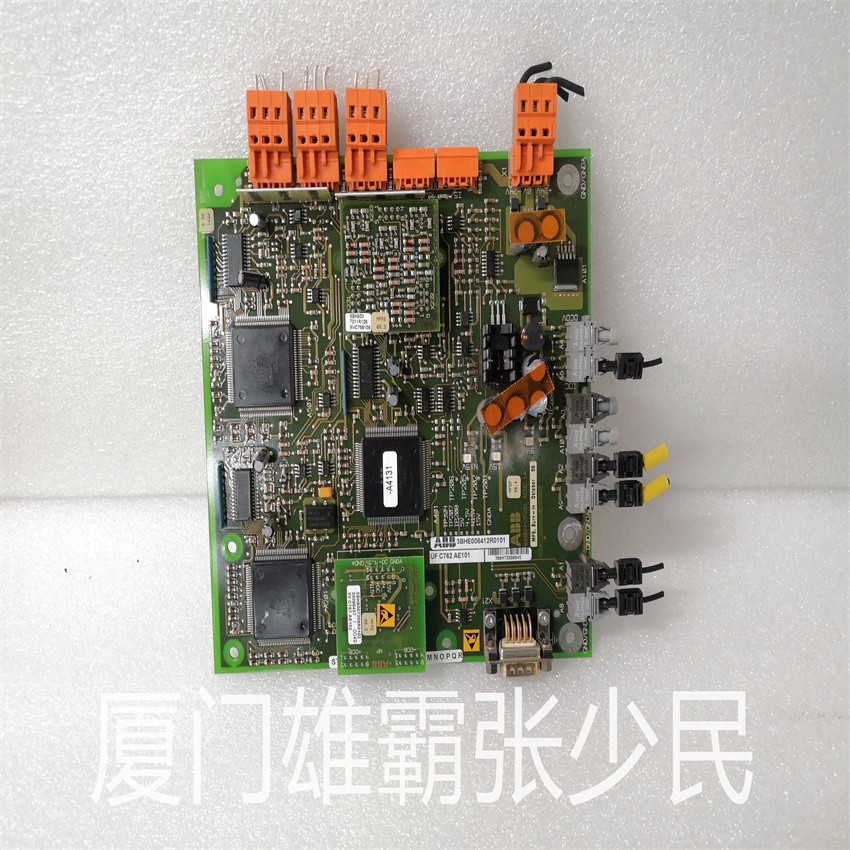

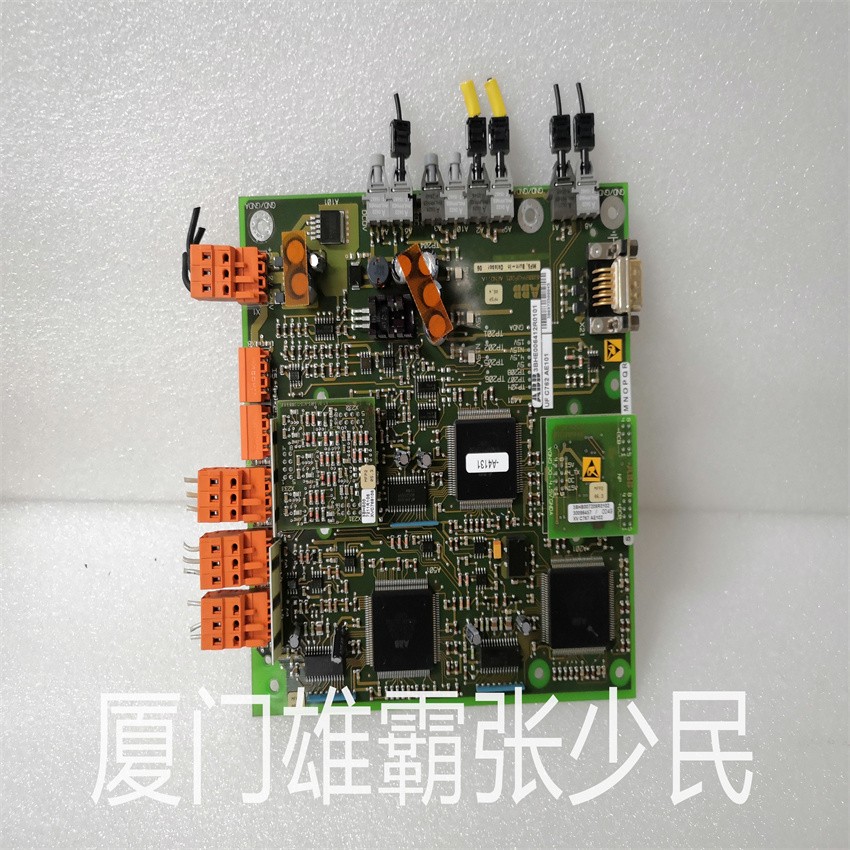

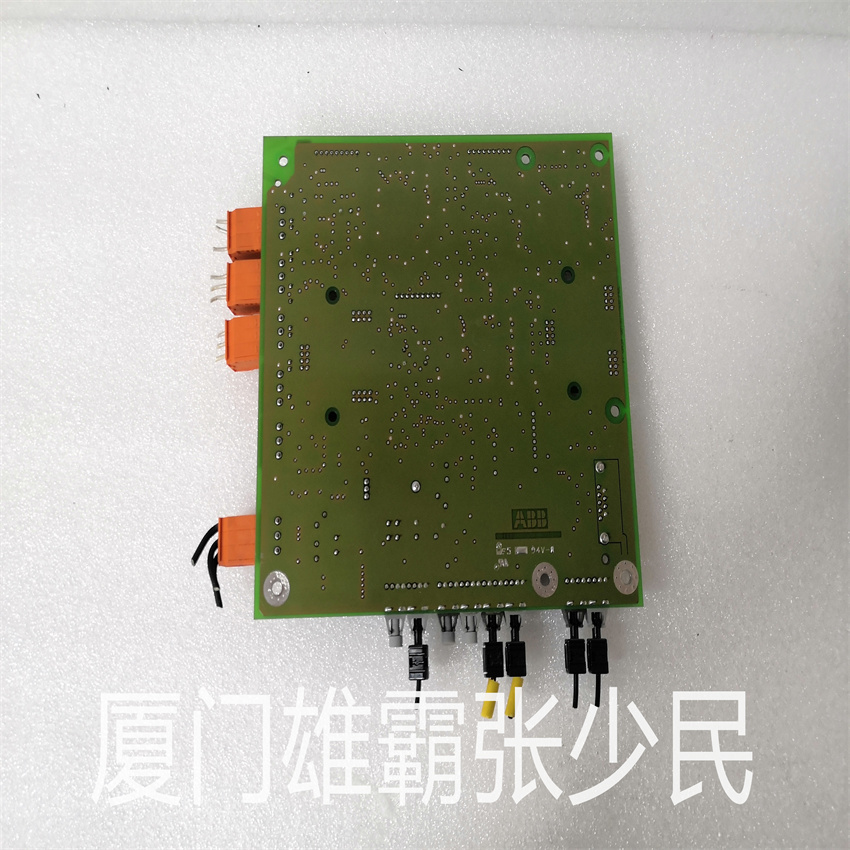

ABB UFC762AE101 3BHE006412R0101 使用成熟的处理核心设计

UFC762AE101 3BHE006412R0101因为计算机制造商早就实现了对称多重处理使用分立CPU的(SMP)设计,关于实施多核处理器架构以及用软件支持它的问题是众所周知的。

UFC762AE101 3BHE006412R0101使用成熟的处理核心设计而不改变架构,可以显著降低设计风险。

对于通用处理器而言,多核处理器的主要动力来自于处理器性能的大幅提升工作频率。这是由于三个主要因素:[11]

这记忆墙;处理器和内存速度之间越来越大的差距。实际上,这促使高速缓存变得更大,以掩盖内存的延迟。这仅在内存带宽不是性能瓶颈的情况下有所帮助。

这ILP墙;越来越难找到足够的单个指令流中的并行性让高性能单核处理器保持忙碌。

这电力墙;随着工作频率的每一个因子的增加,消耗指数增加的功率(因此也产生指数增加的热量)的趋势。这种增长可以通过以下方式缓解”收缩对于相同的逻辑,处理器使用更小的迹线。这电力墙提出了制造、系统设计和部署问题,这些问题在面对由于记忆墙和ILP墙。[需要引用]

为了继续为通用处理器提供常规的性能改进,制造商如美国英特尔公司(财富500强公司之一ˌ以生产CPU芯片著称)和超微半导体公司已经转向多核设计,在某些应用和系统中牺牲较低的制造成本以获得更高的性能。多核架构正在开发中,但替代方案也在开发中。现有市场的一个特别强有力的竞争者是将外围功能进一步集成到芯片中。

UFC762AE101 3BHE006412R0101同一芯片上多个CPU内核的接近性允许缓存一致性电路以比信号必须在片外传输时更高的时钟速率工作。在单个芯片上组合等效的CPU可显著提高的性能缓存窥探(备选方案:总线窥探)运营。简单地说,这意味着信号不同的中央处理器之间传输的距离更短,因此这些信号贬低更少。这些高质量的信号允许在给定的时间段内发送更多的数据,因为单个信号可以更短并且不需要经常重复。13365909307雄霸张少民

UFC762AE101 3BHE006412R0101假设芯片可以在物理上安装到封装中,多核CPU设计需要更少的空间印制电路板(PCB)空间比多芯片SMP设计更大。此外,双核处理器的功耗略低于两个耦合的单核处理器,主要是因为驱动芯片外部信号所需的功耗降低。此外,内核共享一些电路,如L2缓存和的接口前端总线(金融稳定委员会)。就可用芯片面积的竞争技术而言,与设计新的更宽内核设计相比,多核设计可以利用成熟的CPU内核库设计,生产出设计错误风险更低的产品。此外,增加更多的缓存会带来收益递减。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。